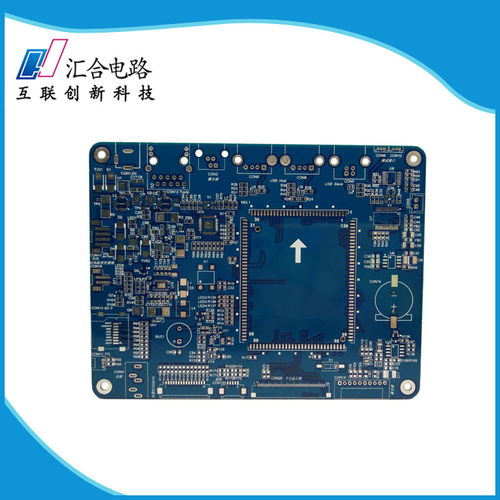

Renesas RZ/A1L系列ARM Cortex-A9 MCU开发方案与PCB电路板设计指南

Renesas RZ/A1L系列微控制器(MCU)基于高性能的ARM Cortex-A9内核,集成了丰富的外设和存储器,广泛应用于工业自动化、人机界面(HMI)、物联网网关等嵌入式系统。为了充分发挥其性能,一个稳定可靠的PCB电路板设计至关重要。本文将详细介绍基于RZ/A1L的开发方案核心要点以及PCB设计中的关键注意事项。

一、Renesas RZ/A1L系列MCU开发方案概述

RZ/A1L系列的最大特点是其大容量片上RAM(高达10MB),无需外接DRAM即可运行Linux等复杂操作系统,这极大地简化了系统设计并降低了整体成本。其主频可达400MHz,具备强大的图形处理能力(支持2D图形引擎和LCD控制器),非常适合需要图形显示的应用。

一个完整的开发方案通常包括:

- 硬件平台:核心板或自定义PCB,包含RZ/A1L MCU、电源电路、时钟电路、启动配置电路、调试接口及必要的外设接口。

- 软件开发环境:Renesas提供的灵活配置软件包(FSP)、GNU工具链、Linux BSP(板级支持包)以及丰富的中间件和示例代码。

- 操作系统支持:除了裸机编程,官方支持Linux、RTOS(如FreeRTOS)等多种操作系统,方便开发者根据应用需求选择。

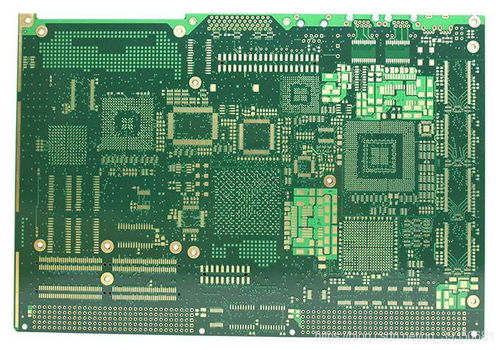

二、PCB电路板设计关键要点

1. 电源设计:

RZ/A1L通常需要多个电源轨(如内核电压、I/O电压、DDR I/O电压、模拟电压等)。必须使用低噪声的LDO或开关电源,并确保上电/掉电时序符合数据手册要求。每个电源引脚附近都应放置去耦电容(通常为0.1μF和10μF组合),且电容应尽量靠近引脚放置,以提供低阻抗的电流路径并滤除高频噪声。

2. 时钟电路:

外部主时钟晶振(通常为12MHz至24MHz)的布局至关重要。晶振应尽可能靠近MCU的XTAL引脚,走线短而直,并在周围铺设接地铜皮进行屏蔽。负载电容的接地回路应尽量短,避免其他高速信号线靠近晶振区域。

3. 启动模式配置:

RZ/A1L通过特定的引脚(如MD[5:0])在上电时采样来确定启动设备(如SPI Flash、eMMC、NAND Flash等)。这些配置引脚需要通过电阻上拉或下拉至明确电平,PCB布局时应确保其连接稳定可靠,避免干扰。

4. 高速信号与存储器接口:

尽管RZ/A1L片上集成大RAM,但若使用外部存储器(如SDRAM、NAND Flash),其接口布线需遵循高速信号规则。对于SDRAM接口,应控制数据线、地址线和控制线的等长(通常以时钟线为参考),并做好阻抗匹配(通常为50Ω)。走线应尽量在同一层,避免过孔,并远离噪声源。

5. 复位与调试电路:

复位信号(RESET#)应使用上拉电阻,且走线应远离高频信号。调试接口(如JTAG或SWD)的引脚应串联小电阻(如22Ω至100Ω)以减小过冲,并靠近板边连接器以便访问。

6. 层叠与接地:

对于中等复杂度的应用,建议至少使用4层PCB板。标准的层叠可以是:顶层(信号)、内层1(地平面)、内层2(电源平面)、底层(信号)。完整的地平面能为高速信号提供清晰的返回路径,是降低电磁干扰(EMI)和保证信号完整性的基础。电源平面应合理分割,确保不同电源域之间隔离。

7. 热设计与外设布局:

RZ/A1L在工作时会产生一定热量,尤其是运行在最高主频时。应在芯片底部或顶部设计足够的散热铜皮,并通过过孔连接到内部地平面以辅助散热。以太网、USB、LCD等外设接口应按照其接口规范进行布局,例如USB差分线(D+, D-)需等长且并行走线,并控制差分阻抗(通常为90Ω)。

,成功开发基于Renesas RZ/A1L系列MCU的产品,一个经过精心设计的PCB是硬件成功的基石。开发者必须仔细研读官方提供的硬件手册、数据手册和应用笔记,在原理图设计和PCB布局阶段就充分考虑电源完整性、信号完整性和电磁兼容性。结合官方强大的软件生态系统,可以高效地构建出高性能、高可靠性的嵌入式解决方案。

如若转载,请注明出处:http://www.okbkj.com/product/10.html

更新时间:2026-04-20 03:31:19